什么是cowos? 用最简单的方式带你了解半导体封装!-yb体育app官网

来源:科技新报 原作者:许庭睿

过去数十年来,为了扩增芯片的晶体管数量以推升运算效能,半导体制造技术已从1971年10,000nm制程进步至2022年3nm制程,逐渐逼近目前已知的物理极限,但随着人工智能、aigc等相关应用高速发展,设备端对于核心芯片的效能需求将越来越高; 在制程技术提升可能遭遇瓶颈,但是运算资源需求持续走高的情况下,透过先进封装技术提升芯片之晶体管数量就显得格外重要。

01

半导体先进封装技术

这两年“先进封装”被聊得很多,“封装”大概可以类比为对电子芯片的保护壳,保护电路芯片免受外界环境的不良影响。当然芯片封装还涉及到固定、散热增强,以及与外界的电气、信号互连等问题,而“先进封装”的核心还在“先进”二字上,主要是针对 7nm 以下晶圆的封装技术; 然而,人工智能浪潮下,带动ai服务器需求成长,也带动英伟达gpu图形芯片需求,而gpu的cowos先进封装产能供不应求,那究竟什么是cowos?

02

什么是cowos?

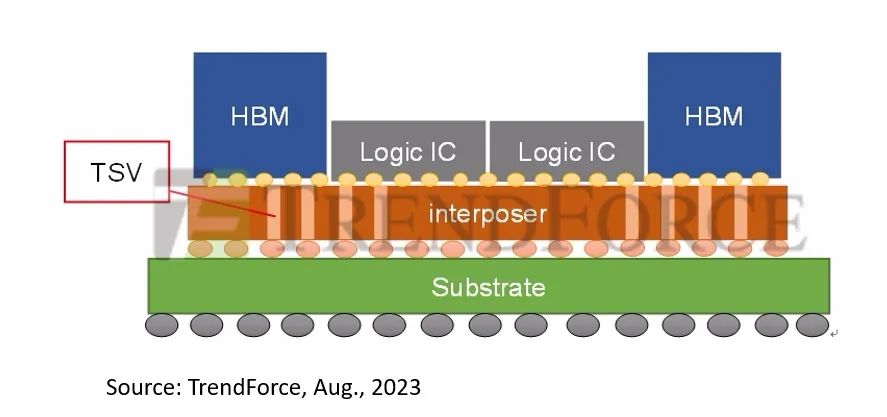

cowos 是一种 2.5d、3d 的封装技术,可以分成“cow”和“wos”来看。“cow(chip-on-wafer)”是芯片堆叠; “wos(wafer-on-substrate)”则是将芯片堆叠在基板上。cowos 就是把芯片堆叠起来,再封装于基板上,最终形成 2.5d、3d 的型态,可以减少芯片的空间,同时还减少功耗和成本。下图为cowos封装示意图,将逻辑芯片及hbm(高带宽存储器)先连接于中介板上,透过中介板内微小金属线来整合左右不同芯片的电子讯号,同时经由“硅穿孔(tsv)”技术来连结下方基板,最终透过金属球衔接至外部电路。

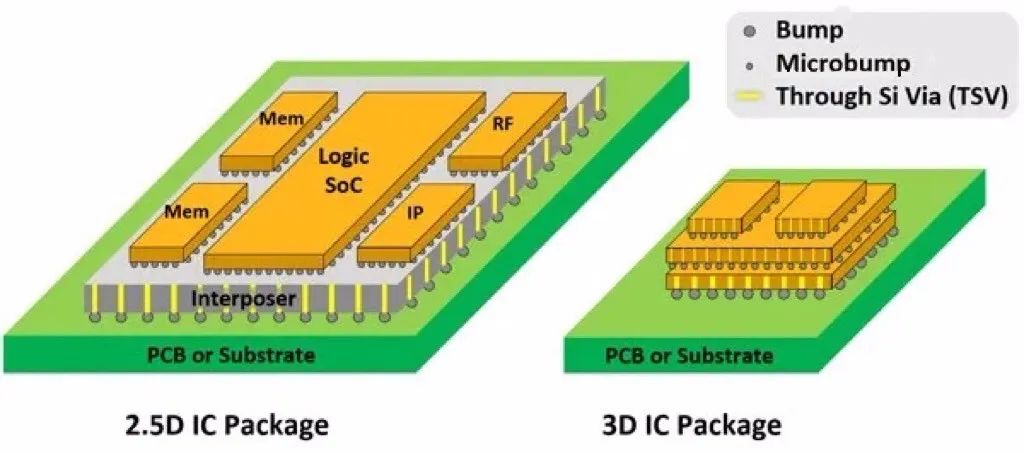

而2.5d与3d封装技术则是差别在堆叠方式。2.5d 封装是指将芯片堆叠于中间层之上或透过硅桥连结芯片,以水平堆叠的方式,主要应用于拼接逻辑运算芯片和高带宽存储器; 3d 封装则是垂直堆叠芯片的技术,主要面向高效能逻辑芯片、soc 制造。

03

先进封装不在封装厂完成?

说到先进封装,首先想到的会是台积电而非传统封测大厂,因为先进封装已经面临到 7nm 以下,而传统封装厂研发速度已无法跟进晶圆制程的脚步,其中 cowos 中的 cow 部分过于精密,只能由台积电制造,所以才会造就这番景象。同时,台积电拥有许多全世界的高端客户,为此“一条龙”的服务更能同时维持制程与封装部分的良率,未来面对高阶客户的交付工作也将更为极致。

04

cowos的应用发展

高端芯片走向多个小芯片、内存,堆叠成为必然发展趋势,cowos 封装技术应用的领域广泛,包含高效能运算 hpc、ai 人工智能、数据中心、5g、物联网、车用电子等等,可以说在未来的各大趋势,cowos 封装技术会扮演着相当重要的地位。

过去的芯片效能都仰赖半导体制程的改进而提升,但随着元件尺寸越来越接近物理极限,芯片微缩难度越来越高,要保持小体积、高效能的芯片设计,半导体产业不仅持续发展先进制程,同时也朝芯片架构着手改进,让芯片从原先的单层,转向多层堆叠。也因如此,先进封装也成为延续摩尔定律的关键推手之一,在半导体产业中引领浪潮。

end

会议预告:经济逆风、消费电子需求不显,半导体身处下行周期中。展望2024年,半导体产业又将迎来哪些变化?2023年11月8日,trendforce集邦咨询将在深圳举办2024存储产业趋势研讨会 ( memory trend seminar 2024)。届时,集邦咨询资深分析师以及行业大咖将带来包括内存、闪存、服务器、晶圆代工等多个议题,全方位剖析半导体上下游产业链发展。欢迎查阅长图了解详情与报名。

封面图片来源:拍信网

微信公众平台

微信公众平台