cxl还不熟,cxl 3.1已经来了!-yb体育app官网

来源:全球半导体观察 原作者:竹子

2019年,英特尔推出了cxl技术,短短几年时间,cxl便成为业界公认的先进设备互连标准,其最为强劲的竞争对手gen-z、opencapi都纷纷退出了竞争,并将gen-z协议、opencapi协议转让给cxl。

目前业界对于cxl的熟识程度远远不及pci-e、hbm等新型存储技术,主要是因为目前pcie还有其适用性,而归根结底是因为该技术发展过于新、发展过于迅速。cxl全称compute express link,是一个全新的得到业界认同的互联技术标准,其可以有效解决内存墙和io墙的瓶颈。pci-e技术是cxl技术的底层基础,cxl则可视为pci-e技术的再提高版本,并且,cxl延伸了更多变革性的功能。

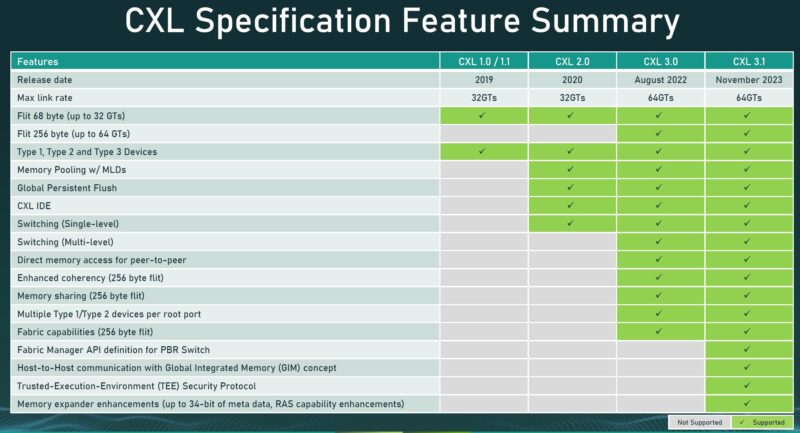

2019年至今,cxl已经发表了1.0/1.1、2.0、3.0/3.1五个不同的版本,cxl2.0内存的池化(pooling)功能较好的实现了以内存为中心的构想;cxl3.0则实现memory sharing(内存共享)和内存访问,在硬件上实现了多机共同访问同样内存地址的能力;而cxl3.1,则具备开启更多对等通信通道的能力,实现了对内存和存储的独立分离,形成独立的模块。并且新规范将支持目前仍在研发中的ddr6内存。

并且对于未来,cxl有着非常清晰的技术发展路线图,业界也对它的未来充满期待。关于cxl技术为何物,读者可以看《大内存时代振奋人心的cxl技术(上)》、《大内存时代振奋人心的cxl技术(下)》,本文将对最新的cxl 3.1进行补充。

关于cxl 3.1

11月末,cxl 3.1新版本正式发布。本次cxl 3.1是对cxl 3.0版本的渐进性的更新,新规范对横向扩展 cxl 进行了额外的结构改进、新的可信执行环境 ehnahcments 以及对内存扩展器的改进。

cxl 3.0于2022年8月推出,cxl 2.0则于2020年推出。总体来看,cxl 3.1的推出速度更快了,也更为适配当前ai浪潮等数据中心的海量存储及运算需求。这次更新不仅提供了更为迅捷、更为安全的计算环境,同时也为将数据中心打造成规模宏大的服务器奠定了更加牢固的技术基础。

国外专业评测网站servethehome发表的《cxl 3.1 specification aims for big topologies》中,对cxl 3.1技术进行了解析。

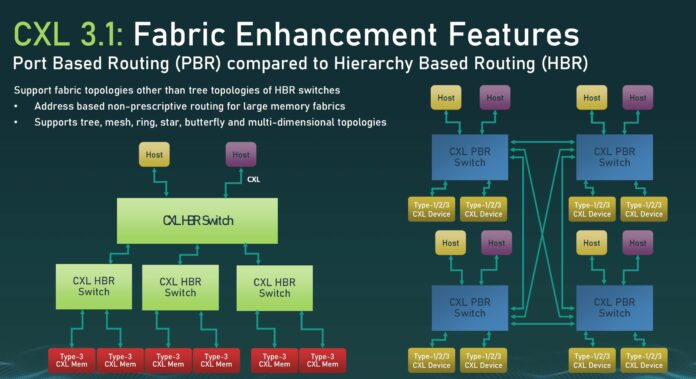

基于 cxl 3.1 结构端口的路由( 图片来源:cxl联盟,下同)

cxl 3.1 在底层进行了许多重大更改,主要是为了解决团队构建更大的 cxl 系统和拓扑时发生的问题。

cxl 3.1 结构增强概述

cxl 3 带来了基于端口的路由 (pbr) 等功能,这与基于层次结构的路由不同,后者更类似于 pcie 树形拓扑。这是促进更大的拓扑和任意通信所必需的。

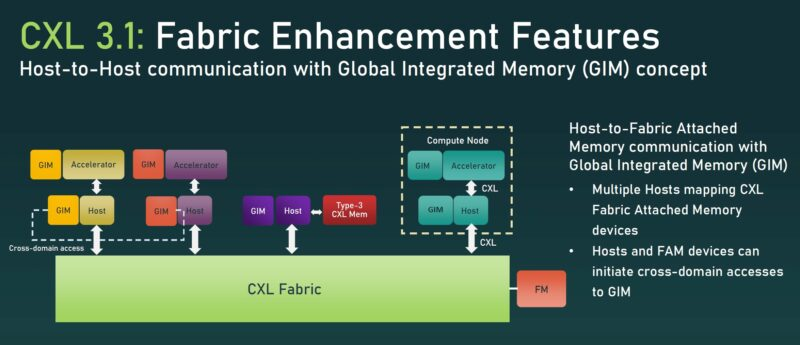

cxl 3.1 的一项增强功能是支持使用全局集成内存 (gim) 通过 cxl 结构进行主机到主机通信。

cxl 3.1 fabric 主机托管全局集成内存

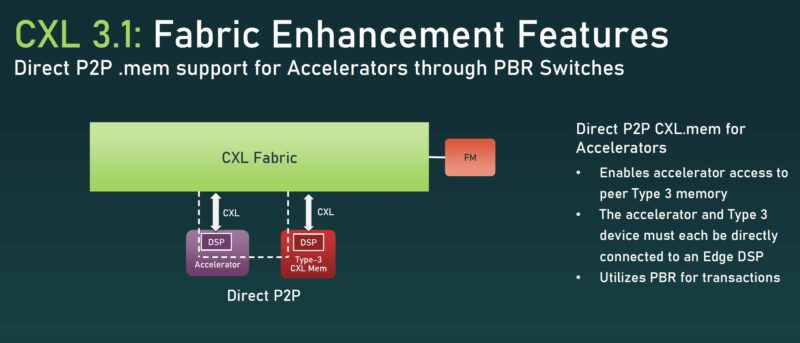

另一大问题是通过cxl对 .mem 内存事务的直接p2p支持。所有关于gpu内存容量的讨论都是ai的限制因素,这将是一种可以将cxl内存和加速器添加到cxl交换机上并让加速器直接使用type-3 cxl内存扩展设备的用例类型。

通过pbr交换机对加速器的cxl 3.1 fabric直接 p2p mem支持

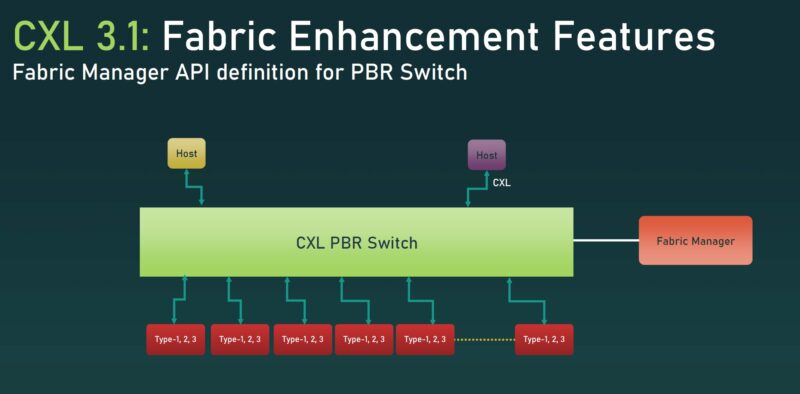

还有针对基于端口的路由 cxl 交换机的 fabric manager api 定义。结构管理器最终可能会成为 cxl 生态系统的关键战场,因为它需要跟踪集群中发生的许多事情。

cxl 3.1 结构管理器 api

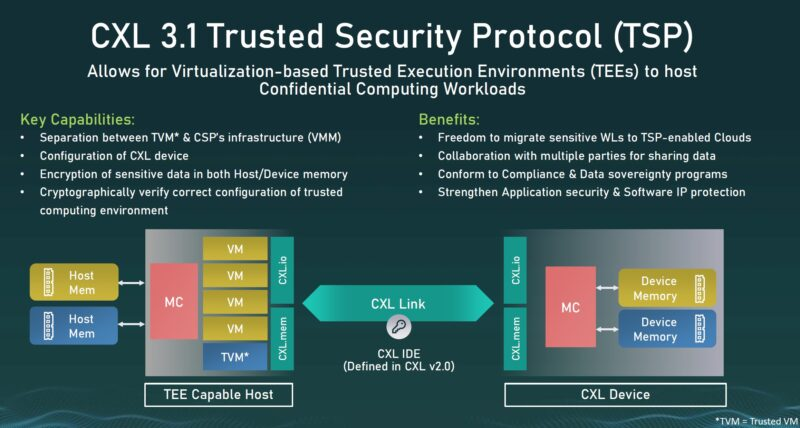

cxl 3.1 可信安全协议 (tsp) 是处理平台安全性的下一步。想象一下,云提供商拥有多租户虚拟机共享通过 cxl 连接的设备。

cxl 3.1 安全可信安全协议 tsp

因此,诸如机密计算之类的当今云虚拟机中的热门话题需要扩展到服务器和连接到结构的设备的范围。

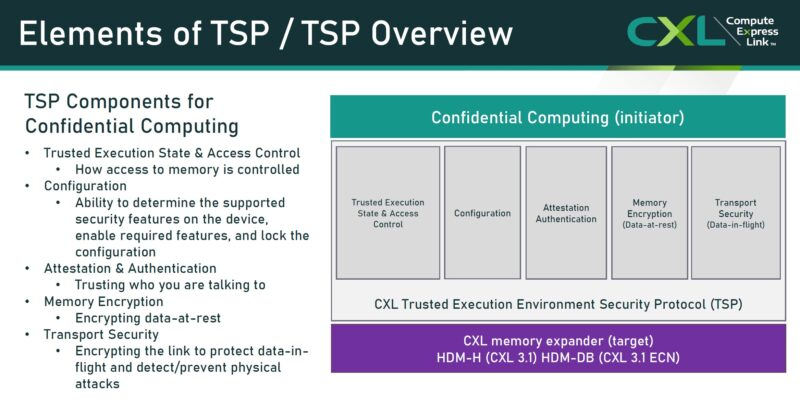

cxl 3.1 tsp 的安全要素

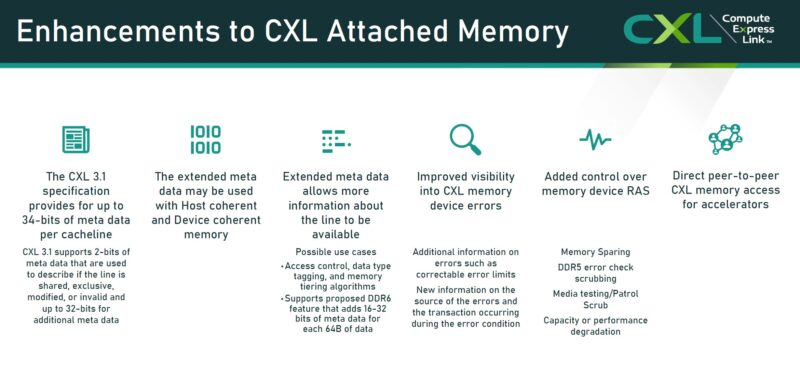

cxl 附加内存还获得了许多 ras 功能以及元数据的附加位。同样,随着拓扑变得越来越大以确保可靠性,这一点很重要。

cxl 3.1支持ddr6

cxl技术的应用场景非常广泛,其中包括数据中心、人工智能和处理器互联等领域。而在数据中心领域,严重的内存问题一直是业界十分头疼的问题。当下存储成本不断增加,以及更为现实的计算和带宽失衡现状使得我们愈加关注内存问题的解决上。

cxl 的主要优点是它允许对直接连接到不同端点的内存进行加载/存储,如此前所述,cxl2.0版本推出了三个十分重要的新功能,分别是可以改变服务器业界生态构型的switching,以及它带来的加速卡(ai、ml和smart nic)和内存的池化(pooling)。

cxl2.0 switching及内存的池化

如上所述,它使得memory polling(内存池)成为可能,你可以跨系统设备实现共享内存池,这就增加了很多的灵活性。比如,如果有机器内存不够时,就可以灵活地在这个池子里寻找内存空间;如果这台机器不需要这些内存了还可以随时还回来。也就是说越靠近cpu的存储器(如dram)将被用来处理更为亟需的工作,这无疑将大大提高内存的使用率,或者降低内存的使用成本。

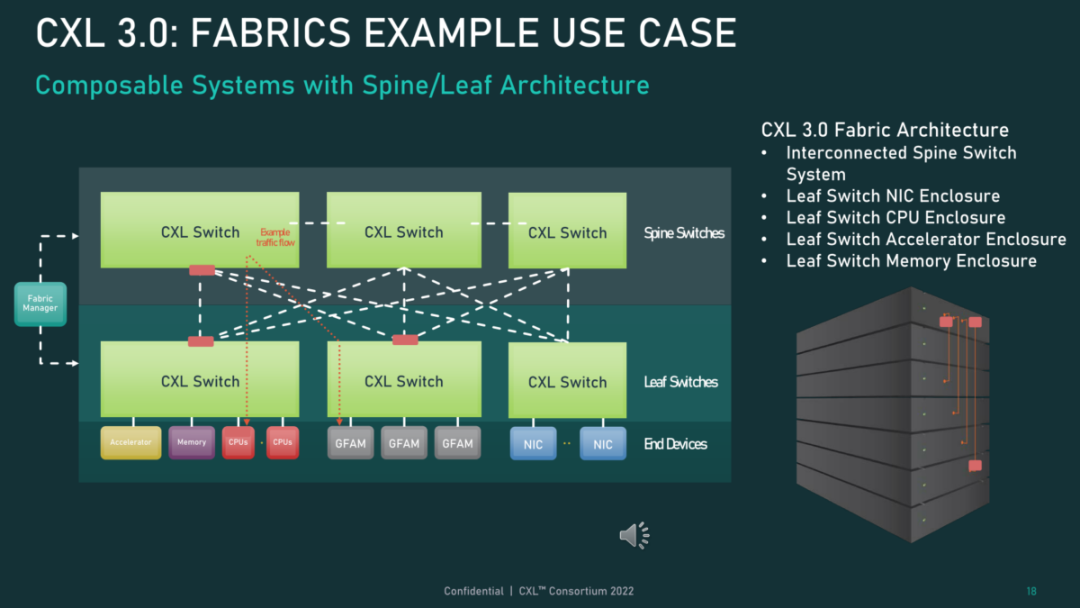

而cxl 3.0又在物理和逻辑层面进行了升级,在物理层面,cxl3.0将每通道吞吐量提升了一倍,达到64gt/s。逻辑层面上,cxl3.0扩招了标准逻辑能力,允许更复杂的连接拓扑,以及一组cxl设备内可以灵活实现memory sharing(内存共享)和内存访问。比如,它可以使得多个switch互相连接,可以使得上百个服务器互联并共享内存。

cxl3.0 memory sharing

memory sharing是非常大的一个亮点,这种能力突破了某一个物理内存只能属于某一台服务器的限制,在硬件上实现了多机共同访问同样内存地址的能力。可以说,cxl的内存一致性得到很大的增强,因为此前的cxl2.0只能通过软件实现memory sharing。

到了最新的cxl 3.1新规范,据悉,其将支持目前仍在研发中的ddr6内存。目前,jedec对ddr6并没有进行详细的讨论。

cxl 3.1 协议可以开放更多点对点通信,将内存和存储分解到单独的盒子中。通过传统网络和互连技术进行分解已经讨论了十年,但 cxl 提供了提供广泛的计算资源所需的可扩展性。

其一,cxl 3.1 规范提供了支持新型内存的机会,并且还可以更有效地将数据重新路由到内存和加速器。

一项重要的进步涉及将结构上的内存资源集中在一个全局地址下。该功能称为全局集成内存,对于在内存和其他资源之间建立更快的连接非常重要。

加速器还能够直接与内存资源通信。基于端口的路由的新功能有助于更快地访问内存资源。

cxl 3.1 内存增强

在《cxl 3.1 specification aims for big topologies》一文中,该作者表示,对于未来的发展,cxl 3.0/ cxl 3.1 就产品而言仍然远远不够,因为该规范是为连接数千个cxl设备而设计的,而现状是我们今天正在用数万个加速器构建人工智能集群。在cxl 世界中,连接的cxl设备可能比当今的加速器更多,其认为cxl在未来或需要扩展。

封面图片来源:拍信网

微信公众平台

微信公众平台