这场dram技术困局谁来破?-yb体育app官网

来源:全球半导体观察 原作者:王凯琪

据全球半导体观察不完全统计,由dram与nand flash所主导的传统存储市场规模已超过1600亿美元,其中最大的内存细分市场dram,正逼近当前技术材料和工艺使用的基本物理极限。

从1998年三星生产出最早的商用ddr sdram芯片,再到ddr1、ddr2、ddr3、ddr4的延续,然后是即将登台唱戏的ddr5和正在研发的ddr6,20多年时间里,dram技术一直在突破向前。

当下新的技术yb体育app官方下载的解决方案如euv光刻、hbm、3d dram、无电容dram等逐渐浮出水面,dram进入到下一个发展阶段,其未来技术路线如何呢?

壹

何为dram和ddr?

在探讨dram技术未来如何演变前,我们先对dram和ddr的概念进行理清。

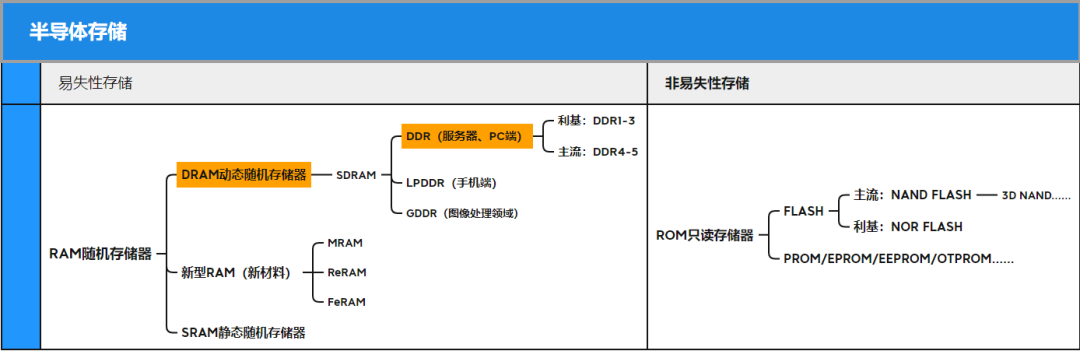

在半导体存储器中,按照电源关断后数据能否被保存可分为rom(read only memory只读存储器,关闭电源仍可保留数据)和ram(random access memory随机存储器,关闭电源即丢失数据)。位于ram之下,又可分为sram(静态随机存储器)、dram(动态随机存储器)以及新型ram(基于新材料研制而成,尚未实现商业化)三大类。

△全球半导体观察根据公开信息整理

基于dram这一支后,又连续衍生了sdram(synchronous dram,同步动态随机存储器)和ddr sdram(double data rate sdram,双倍速率sdram,简称ddr),从历史沿革上,ddr可以说是sdram的升级版本。

按照不同的应用场景划分,固态技术协会(jedec)把dram分成标准ddr、lpddr、gddr三类,其中ddr主要应用于服务器和pc端,lpddr主要应用于手机端和消费电子,gddr的主要应用领域为图像处理领域。目前从它们发展情况,三者虽然存在一定的竞争,但是更多是互为借鉴成长。

今天我们讨论的焦点则侧重于ddr端。

ddr内存建立的初衷是为了加快内存的传输速度,从而弥补内存带宽上的不足,其关键的技术就是双倍数据速率以及预存取。业界数据显示,在一个时钟周期中,ddr可以完成sdr两个周期才能完成的任务,所以在理论上同速率的ddr内存与sdr内存相比,性能要超出一倍,这也是为何sdram在所处的那个时代,即便内存带宽已相当出色,却仍旧被ddr后来居上的原因。

从市场的角度看,dram则分为主流dram和利基型dram(其指从主流规格退役的dram产品,目前主要是ddr3及ddr2,或中低密度容量的产品,多属于客制化存储晶圆)。

在主流dram市场格局上,以三星、美光、sk海力士三分天下,目前具备ddr5/lpddr5量产能力的也仅为上述三家。此外,中国台湾存储企业华邦及南亚科技,以及大陆存储企业长鑫存储的定位也在主流dram市场。

而利基型dram市场的玩家则相对分散,除了三星、美光、海力士之外(三星已在2021年q4确定停产ddr2,同时三星及海力士计划逐步退出ddr3市场),还包含南亚科、华邦等公司。

贰

主流dram技术演进,ddr1-ddr6

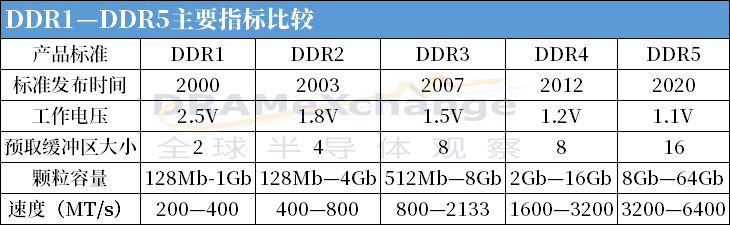

目前已推出的ddr1-ddr5是由固态技术协会(jedec)制定的产品标准。从ddr1到ddr5演变看,ddr的能耗越来越低,传输速度越来越快、存储容量也越来越大;而从制程工艺的进展来看,早前产品的更新时间大致在3到5年更新一代,在步入20nm以内的制程后,ddr在制程上的突破进展呈现放缓趋势。

△全球半导体观察根据公开信息整理

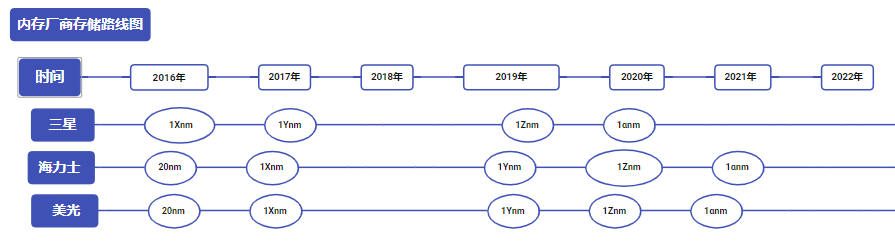

不同于半导体其他工艺直接使用确切数字表达制程的方法,存储行业近年通常使用1x、1y、1z、1α、1β、1γ之类的术语表达制程。对此,美光表示,这种改变很大程度上是因为确切的数字与性能没有很好的相关性。电路结构是三维的,使用线性的衡量方式并不适合。

业界认为,10nm~20nm系列制程至少包括六代,1x大约等同于19nm,1y约等同于18nm,1z大约为16-17nm,1α、1β、1γ则对应12—14nm(15nm以下)。

据悉,三星电子、sk海力士和美光已在2016~2017年期间进入1xnm阶段,2018~2019年进入1ynm阶段,2020年后进入1znm阶段。目前,各大厂家继续向10nm逼近,目前最新的1αnm仍处于10 nm阶段。

△全球半导体观察根据公开信息整理

从过往历史看,每代ddr新标准发布后都需要经过2年左右的优化,才能实现性能的较为全面的稳定提升,而后实现对上一代产品的市场替代则可能需要3到5年的时间。业界数据显示,ddr3和ddr4都享有大约7年的生命周期。ddr4存储器标准于2012年发布,而其初代产品则于2014年入市,直到2016年才实现了市场份额的大幅提升。

对于最新一代的ddr5而言,其最新款产品产能还处于爬坡期,售价还较高,性能也未发展到最优。业界预测今年将是ddr5的预热年,而从明年开始,ddr5渗透率将大幅提升。并且由于ddr技术愈发成熟,ddr5的保质期或比ddr4长。

从推出ddr5标准至今已有两年时间,jedec最近也对ddr5标准 (jesd79-5a)进行了更新,包括密集型云和企业数据中心应用驱动的需求要求,为开发人员提供了两倍的性能和大大提高的能效。为了更高的密度和更高的性能,ddr5有望采用最先进的dram单元技术节点,例如d1z或d1a (d1α)代,这是10纳米级dram节点的第3代或第4代。ddr5内存包含多项创新和新的dimm架构,可实现速度等级跳跃并支持未来扩展。

随着ddr5内存逐渐进入市场,三星又已在马不停蹄的开发下一代ddr6内存,并预计在2024年之前完成设计。在今年7月召开的研讨会上,三星证实将采用msap技术研发加强下一代ddr6内存的电路连接,并将适应ddr6内存中增加的层数。就规格而言,ddr6内存的速度将是现有ddr5内存的两倍,传输速度可达12800 mbps(jedec),超频后的速度可超过17000 mbps。

叁

哪一条会是dram的未来演进之路?

由于现存的dram技术正不断逼近当前技术材料和工艺使用的基本物理极限,关于ddr6技术亦或是dram的未来技术探讨远不止于此,以下将对euv光刻、hbm、3d dram、无电容dram技术进行说明。

1

确信的一步,euv光刻机的成熟运用

对于dram厂商而言,利用euv光刻机迈入到10nm工艺路线已经成为确信的一步,目前三星、sk海力士和美光三大dram厂商已先后采纳euv技术。

trendforce集邦咨询分析师吴雅婷表示,使用euv光刻技术是dram制程微缩的必经之路,具体有三大好处:

一是可以使dram制程进一步微缩至15nm以下;

二是通过更先进制程的递进,单颗颗粒的容量向上提升至16gb或更高;

三是生产制程时间缩短,因为其要曝光的道数可以减少。

三星最早引入euv光刻。2020年3月,三星率先使用euv光刻技术,同年10月便开始批量生产基于euv的14nm dram。在此过程中,三星将其最先进的14nm ddr5上的euv层数从两层增加到了五层dram工艺。今年2月,三星官方表示其基于极紫外(euv)光刻技术的1z-nm工艺的dram已完成了量产。业界消息显示,三星还将继续为下一代dram增加euv步骤,其三星的p3工厂也将采用euv工艺生产10nm dram。

sk海力士引入euv是在2021年。2021年2月,sk海力士完成首个用于dram的euv晶圆厂m16,正式引入了euv光刻设备。2021年7月,sk海力士宣布量产了1a nm工艺的8千兆的lpddr4 euv dram。

官方消息显示,与第三代1z nm内存芯片相比,1a技术在相同的晶圆面积下,生产的芯片数量可以增加25%。此外,2021年sk海力士还发布了据称是业界性能最高的ddr5 dram,作为海力士的第三代高带宽内存,该芯片被称为hbm3。

对比前两家的早早加码euv,美光方面则稍晚一些。据外媒此前消息,美光计划从2024年将euv纳入dram开发路线图,结合今年6月美光董事长卢东晖的发言,其a3厂将会在今年下半年导入euv设备,为美光1γ dram早日量产预做准备。

值得注意的是,与三星和sk海力士相比,美光在2021年便推出了其1anm内存节点dram,推出该工艺时,美光依旧未使用euv光刻技术,美光称其存储密度比之前的1z nm节点dram提高40%。

厂商对于euv设备何时引入的考量的重点还在于成本。公开消息显示,asml正在着手研发的新旗舰光刻机造价十分高昂,价值便达到4亿美元(约合人民币26.75亿元)。现下尖端dram是基于大约12~15纳米的最小节点,这时引入euv光刻机时机已经成熟。

2

挑战极限,3d dram有望接棒

euv光刻机解决的仅仅是眼下的难题,面对当下的瓶颈,dram厂商的长远命题是材料和架构的突破。

当下,努力通过迁移到3d来颠覆平面dram技术成为了dram厂商解决困境的共识,这便是3d dram技术,其甚至被称之为未来十年的命题。

dram工艺之所以提升越来越难,还需要回归到它的结构上。dram是基于一个晶体管和一个电容器的存储单元。其扩展是在一个平面上,将每个存储单元像拼图一样拼接起来。要想提升dram工艺,电容器的缩放是一个挑战。另一个挑战是电容到数字线的电荷共享,要考虑用多少时间将电荷转移到数字线上、数字线有多长。

既然在一个平面内塞入更多存储单元很困难,那么将多个平面叠起来行不行?这就是3d dram,一种将存储单元堆叠至逻辑单元上方,以实现在单位晶圆面积上产出更多产量的新型存储方式。除了晶圆的裸晶产出量增加外,使用3d堆叠技术也能因为可重复使用储存电容而有效降低 dram的单位成本。

3d堆叠技术可在nand发展上有所借鉴,3d nand flash早在2015年就已步入3d堆叠,并开始朝着200 层堆叠过渡,然而dram市场却仍处于探索阶段,为了使3d dram能够早日普及并量产,各大厂商和研究院所也在努力寻找突破技术。

3

曲线突围路径,突破这堵内存墙

另外,许多厂商也对内存处理方法进行了研究。据悉,当前的数据处理方案依赖于数据存储与数据处理分离的体系结构,这需要不断地在内存中来回传输信息,较为耗费时间和精力,且随着当下数据以指数函数陡升下,性能成本也不断上升。

突破内存墙的设想便是通过开发不同的接口和协议,从而显著提高信息传输的效率。其中新型内存处理技术hbm(high bandwidth memory,高带宽存储器)技术以及作为“外部存储器”互连而获得采用的compute express link(cxl)在当下获得的认可度较高。

hbm技术是通过tsv技术进行芯片堆叠,以增加吞吐量并克服单一封装内带宽的限制。其能充分利用空间并缩小面积,并且突破了内存容量与带宽瓶颈。其也因为dram和cpu/gpu物理位置的接近使得速度进一步提升。业界消息显示,目前hbm2在很大程度上是gddr6的竞争对手。不过从长远看,因为2d在制造上接近天花板,dram仍有很强的3d化趋势。

cxl则是一种开放标准的行业支持的缓存一致性互连,用于处理器、内存扩展和加速器的链接。从本质上讲,cxl技术维护cpu内存空间和连接设备上的内存之间的内存一致性,这可以实现资源共享(或池化)以获得更高的性能,降低软件堆栈的复杂性,并降低整体系统成本。简单而言就是可以提供更大的内存空间,目前在这一块上的玩家主要有三星、英特尔、sk海力士等。

4

新的研究方向,无电容dram

除了以上所述技术外,业界近年也开始在无电容技术方面下功夫,试图借此解决目前的难题。关于无电容,早有dynamic flash memory、vlt技术、z-ram等技术出现,但日前,美国和比利时的独立研究小组imec在2021 iedm上展示了一款全新的无电容器dram,这种新型的dram基于igzo(indium-gallium-zinc-oxide)可以完全兼容300mm beol (back-end-of-line),并具有>103s保留和无限 (>1011) 耐久性。

总体而言,无论是哪种方法,均遵循着两种路径,要么是在先进封装上下功能,要么是在先进制程上苦心钻研。两条路径相辅相成,缺一不可。

结 语

dram存储早已渗透到现代生活的方方面面,当下所有以数据为中心的基础设施都迫切需要更高级智慧的半导体内存和存储技术,这也是dram为何吸引如此之多目光的原因,其深刻关乎着未来相关技术前进的步伐。技术发展日新月异,但是总能从历史的车轮中看到其行进的道路。当下dram又走到了技术发展的十字路口,不破不立,未来dram将会走向何方呢,我们拭目以待。

tss 2022亮点剧透

在即将举办的2022集邦咨询半导体峰会暨存储产业高层论坛上,trendforce集邦咨询半导体资深研究副总经理郭祚荣将针对《通胀与后疫情下的2023年内存产业发展趋势》发表主题演讲,敬请期待。

封面图片来源:拍信网

微信公众平台

微信公众平台